- 퍼갈 때 2차 출처 표시바람.

- 노출 정보에서 AMD가 삼성 4nm 공정으로 작업하는 내역이 나와서 어느 제품인지 검토해봄.

32Gbps, 2GHz, 7nm/5nm

Infinity Fabric의 die-to-die 커넥트 인터페이스인 GMI3(IFOP) 내용으로 보임.

클럭 2GHz는 Zen4 이상인데 Zen4 기본 스펙은 1733MHz임.

Data rate 32Gbps를 보면 에픽9004 스펙 시트에는 32Gbps로 나오는데 발표 슬라이드에는 36Gbps임.

(https://www.amd.com/system/files/documents/58015-epyc-9004-tg-architecture-overview.pdf)

양쪽 다 최대 2GHz, 36Gbps를 보증하지만 제품에 따라 다르게 스펙을 설정했다고 해석할 수 있고,

5nm/7nm는 각각 Zen4 제품의 CCD(TSMC 5nm) / IOD(TSMC 6nm)로 보는게 타당함.

실제 Zen4 라이젠 fclk 오버클럭은 2000 정도가 한계선임.

36Gbps, TSMC 5nm/3nm

36Gbps, 5nm는 Zen4 CCD로 볼 수 있음.

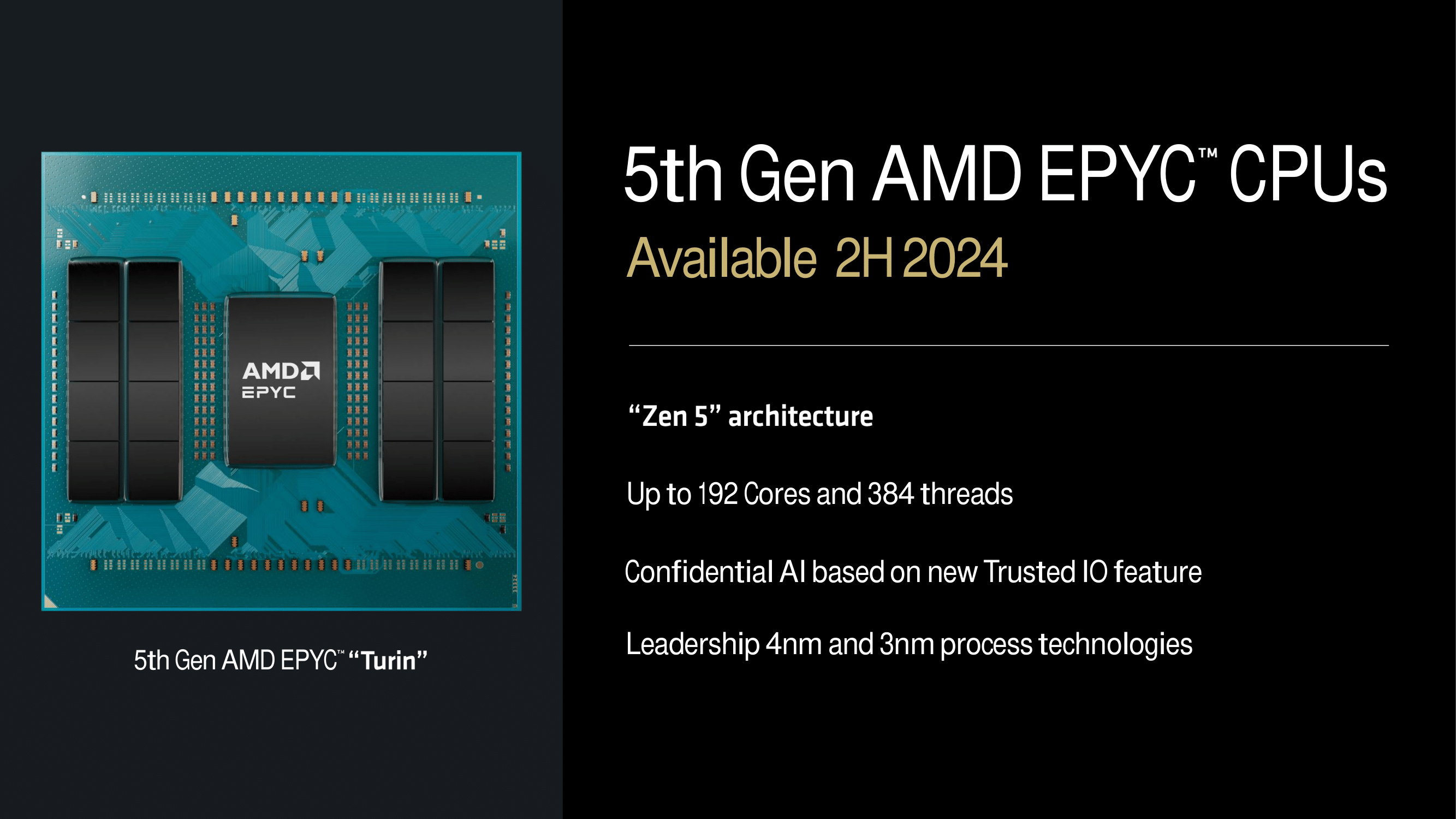

Turin(5세대 EPYC) 발표 내용으로 보아 3nm는 Zen5c CCD로 추측됨.

Zen5 클라이언트 라인 IOD 공정이 Zen4와 같은 6nm인 것도 그렇고, 여전히 36Gbps인걸보면 Zen5에서 여전히 GMI3를 쓴다고 볼 수 있음.

36Gbps, 삼성 4nm

(파운드리 단신 (2022.12.21. 삼성, AMD, 구글, 애플))

32Gbps, 삼성 4nm

Data rate 수치를 보면 AMD에서 삼성 4nm 공정으로 GMI3 인터페이스가 포함된 칩을 설계했다고 볼 수 있음.

그리고 속도로 보아 Zen4(c) 혹은 Zen5(c)에 대응되는 제품임.

이제까지 발표된 제품, 공정으로 소거해보면 남는건 Turin의 IOD만 남음.

그렇다면 Turin IOD를 삼성 공정으로 생산한다는 가설을 뒷받침할 근거가 있을까.

Zen4 EPYC을 보면 IOD는 TSMC 6nm 공정으로 GMI3 인터페이스가 12개있음.

CCD에는 GMI3 인터페이스가 2개있지만 IOD의 GMI3 개수때문에 CCD 12개, 8개인 제품은 CCD-IOD간 커넥션이 1개 (GMI3-Narrow) 이고, CCD 4개인 제품은 커넥션이 2개(GMI3-Wide)임.

물류정보에 나온 Turin 사양을 보면 최대 192코어(12CCD+1IOD), 128코어(16CCD+1IOD)가 있음.

192코어는 Zen5c이고 (12CCD x 16core/CCD), 128코어는 Zen5임. (16CCD x 8core/CCD)

컴퓨텍스에서 했던 Turin 발표를 보면 이미지를 공개한 제품은 12CCD이고 3nm 얘기가 나오고 IOD는 6nm라고 했음. Zen5c 기반 제품에 대한 얘기만 나오고 Zen5 기반 제품에 대한 언급은 없었다고 볼 수 있음.

그리고 IOD가 6nm인 점, 최대 12CCD 사양이란 점에서 전 세대 IOD를 그대로 썼다고 추측할 수 있음.

만약 그렇다면 Zen5 기반 Turin은 최대 16CCD이기때문에 GMI3 인터페이스 부족으로 같은 IOD를 쓸 수 없고,

16개 이상의 GMI3 인터페이스를 갖는 새로운 IOD를 투입해야됨.

Zen5 기반 64코어(8CCD+1IOD) 제품 물류정보에 Wide가 들어간 것도 새로운 IOD가 존재하는 증거로 볼 수 있음.

GMI3가 16개면 8CCD부터 GMI3-Wide 커넥션이 가능하기때문.

- 2024.09.02. 추가

이미지이지만 Zen5, Zen5c 기반 EPYC 패키지가 공개됐었음.

지금까지 알려진 SP5 소켓 사이즈(72mm x 75.4mm), Zen5 CCD 사이즈(오차가 있지만 다이 측정치가 9.05 x 7.76= 70.2mm2)를 기초로 이미지의 각 다이 사이즈를 측정해보면 다음과 같음.

Zen5 Turin IOD : 16.4 x 26.1 = 427mm2

Zen5c Turin dense CCD : 5.8 x 15.0 = 87.1mm2

Zen5c Turin dense IOD : 16.6 x 26.0 = 430mm2

Zen4, Zen4c 기반 에픽 IOD 사이즈가 24.8 x 15.6 = 386.9mm2 였음.

AMD에서 실제품 이미지를 그대로 슬라이드에 담았다면 Turin, Turin dense는 같은 IOD를 사용하고, 전 세대 에픽 IOD보다 큼.

Turin dense IOD 공정을 TSMC 6nm라고 발표했는데 그렇다면 Turin IOD도 같은 다이인 것이고,

5세대 에픽 IOD는 계속 TSMC 6nm 공정을 쓰지만 규모를 키운, 전 세대와 다른 다이라고 봐야함.

삼성 4nm 작업 내용이 IOD가 맞다면 최소 Zen6 세대는 되어야하고 그 때까지 GMI3를 사용한다는게 됨.

- 추정 결론

종합하면 Zen5c 기반 Turin (Turin Dense)는 전 세대 IOD를 그대로 썼지만

Zen5 기반 Turin은 GMI3 인터페이스가 증가된 새로운 IOD를 썼을 것이고 이것이 삼성 4nm 공정으로 생산됐을 가능성이 있음.

Zen5 기반 에픽은 전 세대와 공정은 같지만 규모를 키운 (TSMC 6nm) IOD를 쓰고

Zen6 기반 제품에 삼성 4nm 공정 IOD가 들어갈 가능성이 있음.

'CPU > AMD' 카테고리의 다른 글

| 동클럭 성능 비교, 라노(Llano) vs 프로푸스(Propus) (2) | 2011.08.26 |

|---|---|

| AMD, Fusion APU 신모델 추가.(E450, E300, C60) (0) | 2011.08.23 |

| 저전압 셋팅을 통한 라노의 소비전력 감소. (8) | 2011.07.08 |

| A8-3850으로 보는 AMD APU Llano (4) | 2011.07.06 |

| AMD Bulldozer 라인업, 정보, 성능루머. (0) | 2011.03.20 |

댓글