- 결론부터 말하면 조작 가능성이 없진 않은데 혹시 모르니 재미삼아 이거저거 따져봄.

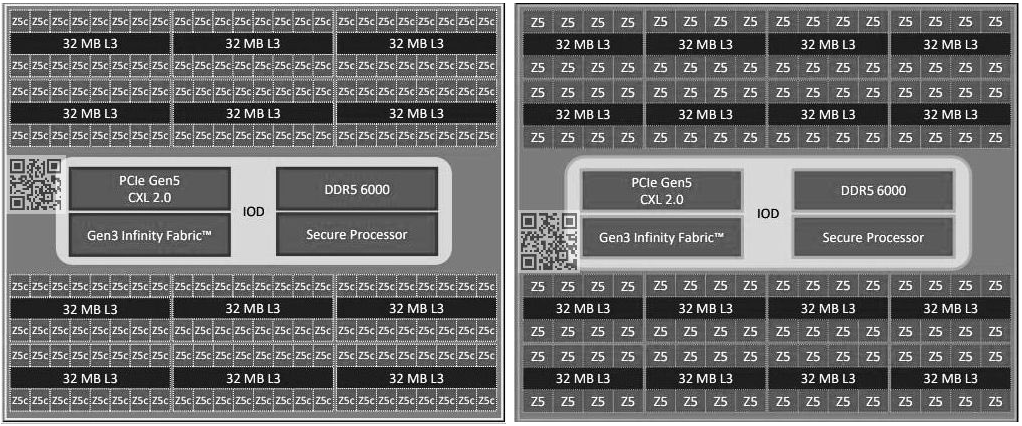

- 베니스(Venice) 기반 에픽 블록 다이어그램?

(https://c.tieba.baidu.com/p/9692193930#)

별 다른 코멘트없이 이미지만 올라와있는데 누가봐도 위는 Venice 같고 밑은 CCD, IOD 다이어그램으로 보임.

CCD는 12코어이고 베니스니까 코어마다 Z6(Zen6)로 써있는거 같고, 가운데는 어설픈 이미지 보정때문에 뭉개져있지만 48MB L3로 추측됨.

IOD에 P는 PCIe일거 같음.

디테일에 약간의 차이가 있지만 기존의 AMD 에픽 이미지와 유사함.

- 정보?

일단 확인되는건

Zen6 CCD는 12코어이고 L3 캐시는 48MB

에픽에 IOD가 최소 2개, CCD가 최소 8개 들어감.

- Zen6 루머

현재까지 나온 Zen6 관련 제품 루머를 정리해보면 다음과 같음.

클라이언트용 CCD에 Zen6 12코어, L3 캐시 48MB가 포함됨. (75mm2)

서버용 CCD는 32코어(175mm2)이고 베니스 기반 에픽은 최대 8CCD, 2IOD 구성으로 최대 256코어.

(초기 루머에서는 32코어 CCD x8 + IOD x4 구성 얘기도 있었음.)

CCD, IOD 개수를 조절해서 다양한 에픽 라인업을 구성하고 인터포저를 통한 IOD간 인터커넥터가 존재.

메모리 12채널/16채널

- 교차 검증

CCD 사양 정보는 루머와 일치함.

CCD에 포함된 코어 개수는 미묘하게 루머와 안 맞는데 둘을 절충해서 Zen6 CCD는 12코어, Zen6c CCD는 32코어라고 볼 수도 있음.

상식적으로 생각해봐도 Zen5 CCD가 8코어인데 갑자기 32코어로 늘어날거로 보기 어려움.

사실 32코어 CCD 루머도 의심스러운게 에픽에 들어가는 16코어 Zen5c CCD 면적이 87mm2 정도인데 다음 세대에 면적을 2배로 늘리는 선택을 할지 의문임.

(AMD IOD의 삼성 4nm 공정 생산 가능성. (24.09.02. update))

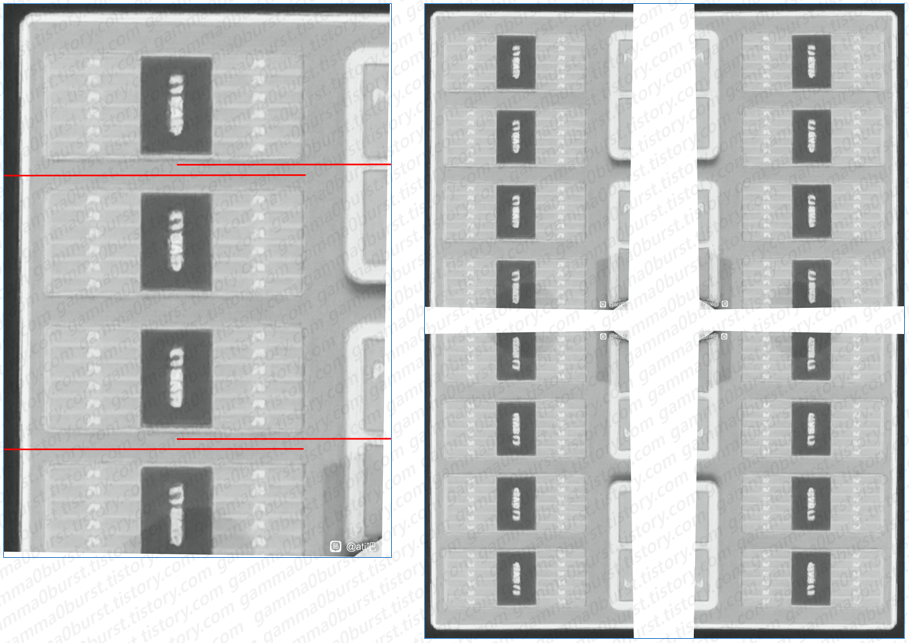

이미지를 다시보면 IOD 중심과 CCD 중심이 안 맞음. (왼쪽)

이런 이미지 만드는데 가운데 정렬은 기본 중의 기본이라 이게 진짜 오피셜 이미지라면 이번에 올라온 이미지를 단순히 좌우대칭한 8CCD+2IOD 구성이 전체 이미지일 가능성은 낮음.

이번에 올라온건 전체 이미지 중 2사분면에 해당하고 전체 이미지는 최소 16CCD+4IOD 구성일 가능성이 높음. (오른쪽)

에픽 사양 측면에서봐도 8CCD일 가능성이 낮음.

Zen5 에픽 최대 사양이 16CCD x 8코어/CCD = 128코어 인데 12코어 Zen6 CCD가 8개면 96코어에 그쳐서 전 세대보다 코어수가 줄어드는, 있을 수 없는 일이 일어남.

전 세대보다 코어수는 무조건 늘어날거기때문에 계산해보면 최소 12CCD(144코어), 일반적으로 전 세대 대비 50% 늘어난 192코어(16CCD)로 예상하는게 타당함.

그러면 오른쪽은 16CCD+4IOD 구성 예상이 맞아떨어지는건데 문제는 굳이 IOD를 4개나 써야하냐는거임.

내부 인터페이스에 변경이 있을 수 있겠지만 기본적인 CCD 개수 지원(GMI 개수)이 이미 16개라서 IOD 1개로도 Zen6 16CCD 지원에 문제가 없음.

끼워맞추자면 IOD도 다이 사이즈에 부담을 느끼기 시작했고 공정 미세화로 면적을 줄이기로 했다고 해석해볼 수 있음.

4세대 에픽 IOD 면적이 387mm2이고 5세대 에픽의 IOD 면적이 430mm2 정도인데 같은 N6 공정임.

세대가 지날수록 요구 사양이 높아지면서 IOD도 점점 커지고 있는건데 이걸 상쇄하려고 6세대 에픽 IOD는 4nm 공정으로 제조한다는 루머가 있음.

삼성 SF4X 공정을 쓰는걸로 알려졌는데 최근 이게 취소됐다는 루머가 나왔는데 삼성 공정을 안 쓴다해도 6nm를 계속 쓰는게 아니라 TSMC 4nm 공정으로 넘어갈걸로 보는게 타당함.

어쨌든 면적, 공정 가격을 종합적으로 고려한 결과가 최신 공정에 가까운 노드를 쓴다는거고 그만큼 서버용 IOD의 거대화가 생각보다 심하다는걸 의미한다고 볼 수 있음.

그렇다면 IOD도 CCD처럼 기능 단위를 작게 나눠서 쓰는 시도를 할만함.

루머와 유출이 다 맞다고 가정하면 6세대 에픽은 다음과 같은 구성임.

Zen6 : 최대 16CCD+4IOD (192코어)

Zen6c : 최대 8CCD+2IOD (256코어) 혹은 8CCD+4IOD (256코어)

'단신 > 단신' 카테고리의 다른 글

| 팹리스, 파운드리 단신. (2025.05.15. 삼성, 구글, AMD) (2) | 2025.05.15 |

|---|---|

| 인텔 노바레이크 프로토타입 정보 노출? (Intel Nova Lake Prototype?) (update 25.05.24.) (3) | 2025.05.14 |

| 팹리스, 파운드리 단신. (2025.03.10. 삼성, 구글) (1) | 2025.03.10 |

| 팹리스, 파운드리 단신. (2025.01.22. 삼성, 구글) (0) | 2025.01.22 |

| 팹리스, 파운드리 단신. (2024.11.23. 삼성, 샤오미, 퀄컴) (1) | 2024.11.23 |

댓글