- 공정 비교 자료 업데이트입니다. (2016.10.29.)

- DAC2016 삼성 자료

DAC2016 발표로 보이는 삼성 자료가 추가됐습니다.

28FD-SOI가 추가되었으며 20LPE는 보이지 않습니다.

애초에 그렇게 공언했기도 했지만 20nm 공정이 징검다리 취급을 받고 있는게 맞는듯 합니다.

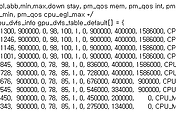

- 45/40nm~28nm 성능 게인

포함하는 공정이 많아지면서 차트가 길어져서 중간에 잘랐습니다.

GF는 자료는 많으나 시기에 따라 내용이 제각각이라 유의미한 결과로 보기 어려워 뺐습니다.

45LP, 40G는 자료가 적어서 안 맞을 수 있습니다.

45nm 이전 공정에 대한 자료가 없습니다.

각 공정에 대한 성능을 공개한지 얼마되지 않아서 그런듯 합니다.

28LPH 등 분명 존재하는 공정이나 차트에서 빠진건 자료가 없기때문입니다.

TSMC는 기본적으로 발표자료를 근거로 했고 28HPM - 20SOC 차이가 6%라는 것만 임의 반영했습니다.

28LP -> 28HPC : +20%, 28HPC -> 28HPC+ : +15% 라는 발표 자료를 반영했습니다.

실제 어떨지는 두고 볼 일.

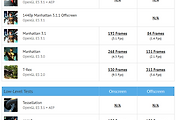

- 20nm~7nm 성능 게인

20LPE에 대한 자료는 크게 두 개입니다.

28LPP -> 20LPE : +20%, 20LPE -> 14LPE : +20%

그런데 28LPP -> 14LPE : +38%는 교차 검증이 된 내용입니다.

각각 28LPP -> 20LPE : +15% 이냐 20LPE -> 14LPE : +15% 이냐라는 선택이 남은거지요.

20SOC와의 차이, 위의 발표 자료에서 20LPE가 빠진걸 고려해서 28LPP -> 20LPE : +15%를 선택했습니다.

DAC2016 자료에서 성능, 전력상 14LPP = 14LPC 로 나왔습니다.

표면적으로는 둘의 차이가 원가 밖에 없게되는데 그렇다면 누가 14LPP를 쓸까요.

단순히 PPA로 드러나지 않는 다른 부분에서 차이가 있을듯 합니다. (TR, 백엔드 라인 구성 등)

14LPP -> 10LPE : +10%, 10LPE -> 10LPP : +10% 라는 공개자료 반영.

이는 DAC2016 자료에서도 교차검증된 내용입니다.

최근에 TSMC 10nm 공정이 16FF+ 대비 성능 +50%, 전력 -40% 라는 내용이 나왔었는데,

(링크 : http://wccftech.com/tsmc-roadmap-7nm-orders-2017-2018/)

현실적으로 이건 특정 전압, 블록에서의 극단적 결과로 생각됩니다.

TSMC 10~7nm 수치는 아래 내용을 근거로 넣었습니다.

숫자가 약간씩 차이가 납니다만, 기본적으로 14/16nm 공정 이후로는 삼성, TSMC간에 Speed 차이는 크지 않은 것으로 보입니다. (전력, 면적은 차이가 있을듯.)

16FF+ -> 10FF(10FF+로 추측) : +20%

16FF+ -> N7 : A72 클럭 +35% (7FF로 반영)

10FF -> N7 : +15~20% (20%로 반영)

'스마트폰 > 삼성 SAMSUNG' 카테고리의 다른 글

| 엑시노스8895 긱벤치4 초기 결과 분석 (Exynos8895, Galaxy S8) (10) | 2017.03.20 |

|---|---|

| 갤럭시 A5,A7 2017 커널 (엑시노스7880) (6) | 2017.02.18 |

| 엑시노스7870/7880 GPU 사양 추정. (Exynos 7870/7880) (8) | 2016.09.03 |

| 엑시노스7570 사양 추정. (Exynos 7570) (6) | 2016.07.31 |

| Zauba 노출 신규 엑시노스 정보. (엑시노스8895, 엑시노스7570) (9) | 2016.07.29 |

댓글