반응형

- 시작하기에 앞서......

잡설이라고 한 것은 제가 잘 모르기때문입니다.

자료나 내용 전개가 중구난방일 가능성이 높습니다.

본문이 100% 맞는다는 보장도 없습니다.

이런 점 참고해서 보시기 바랍니다.

-

-

2013.08.19. Flash Memory Summit 2013 발표 내용 추가.

http://pc.watch.impress.co.jp/docs/column/kaigai/20130819_611653.html

http://pc.watch.impress.co.jp/docs/news/event/20130819_611597.html

2013.08.31. 내용 추가.

http://pc.watch.impress.co.jp/docs/column/kaigai/20130823_612339.html

-

2013년 8월 6일 삼성은 3차원 수직구조 낸드플래시 메모리 양산을 발표했습니다.

(http://samsungsemiconstory.com/434)

3D Vertical NAND 줄여서 3D V-NAND라고 합니다.

몇 가지 내용을 정리해보면,

- 업계 최대 용량 128Gbit

- 3차원 원통형 CTF(Charge Trap Flash)

- 3차원 수직적층. 24단.

- 기존 20nm급 대비 집적도 2배 이상.

- 쓰기속도 2배 이상. (20nm급 Planar 대비)

- 쓰기횟수 2~10배 이상. (20nm급 Planar 대비)

(http://samsungsemiconstory.com/434)

Gate Stack 구조인 것으로 보아 TCAT(Terabit Cell Array Transistor)인듯.

(http://samsungsemiconstory.com/434)

낸드플래시는 셀을 늘려서 용량을 늘리는데 그 동안 수평방향으로 확장을 해왔습니다.

이를 수직으로 쌓아서 면적을 늘리지 않으면서 용량을 늘리는겁니다.

가장 큰 이유는 공정 미세화에 한계가 왔기때문입니다.

10nm급으로 들어서면서 셀 간의 간섭이 심해지고 저장할 수 있는 전자의 양도 줄어들었습니다.

어떤 자료를 보면 최신 공정에서 신호 단계당 전자 수가 10~15개 수준입니다.

전자 10~15개 차이를 읽어내야 저장된 데이터가 어떤 것인지 읽을 수 있다는겁니다.

기존 방식으로 더 이상 집적도를 올릴 수 없는 상황에 왔습니다.

2차원으로 배치된 셀을 수직으로 배치하면 집적도를 극적으로 높일 수 있습니다만, 문제는 생산성이 나오냐는 것.

공정도 복잡해지고 그만큼 수율은 낮아집니다.

이번 삼성의 양산발표가 대단한건 그런 이유때문.

구조에 따른 분류, 소재에 따른 분류 등등 있는데다가 도시바-샌디스크, 삼성, 하이닉스 등등에서 연구 중인 방식도 다 제각각.

삼성이 제일 다양하게 연구개발하고 있는듯 합니다.

구체적인 부분은 모르겠지만 Gate Stack이 Channel Stack보다 제조는 쉬운듯.

(http://techon.nikkeibp.co.jp/article/HONSHI/20090827/174636/?P=1)

(http://techon.nikkeibp.co.jp/article/HONSHI/20090827/174636/?P=1)

(http://techon.nikkeibp.co.jp/english/NEWS_EN/20130613/287618/)

A/R이 단면적/높이 비율일겁니다.

(DRAM의 Capacitor와 공정 미세화 얘기할 때 자주 나옵니다.)

적층 구조이기때문에 전체 구조를 관통하는 구조의 A/R이 커질 수 밖에 없고(수직 방향으로 길어짐.) 제조 난이도가 올라갑니다.

- 업계 최대 용량 128Gbit

기존에도 128Gbit 제품은 있었습니다.

3bit/cell 제품이었지요.

통칭 TLC, 삼성에서는 3bit MLC라고 부르는 제품입니다.

2bit/cell (MLC) 제품은 최대 64Gbit 였습니다.

도시바에서 학회에서 발표한 3D 낸드를 보면 256Gbit, MLC이고 세로로 24개의 트랜지스터를 적층했습니다.

도시바는 자사의 3D낸드 구조를 BiCS(Bit Cost Scalable)이라고 하는데 삼성의 3D낸드와 비교하면 바탕이 되는 컨셉은 같습니다. Gate Stack 이지요.

MLC라고 합니다.

- 기존 20nm급 대비 집적도 2배 이상.

30nm 급이라고 합니다.

집적도 2배.

공정 노드만 보면 집적도는 V-NAND쪽이 러프하게 2배정도로 낮습니다.

수직의 채널구조의 단면이 어느 정도인가가 의문인데,

수직으로 24개 셀이 적층되었으니 앞서 말한 공정 노드에 의한 집적도 차이까지 반영하면 집적도는 12배가 됩니다.

실제 집적도는 2배 이상이라고 하는걸보면 수직 채널의 단면이 평면구조 셀 면적의 6배 이하라고 봐야겠지요.

채널 단면적은 평면셀 면적의 2~2.5배정도인듯 합니다.

- 쓰기속도 2배 이상. (20nm급 Planar 대비)

- 쓰기횟수 2~10배 이상. (20nm급 Planar 대비)

쓰기속도 2배.

소비전력(읽기/쓰기) 46% 감소.

Program/Erase 내구성 10배.

Program/Erase cycle이 35,000으로 크게 늘었습니다.

20nm급 MLC가 3000

30nm급 MLC가 5000

50nm급 MLC가 10000

정도로 알려져 있습니다.

SLC가 100,000 으로 알려져 있으니 30nm급 MLC임을 생각하면 내구성이 크게 향상되었습니다.

- 3차원 원통형 CTF(Charge Trap Flash)

적층 구조에 일반적인 Floating Gate를 적용하면 구조적으로 복잡해지고 공정은 훨씬 더 복잡해지겠지요.

Floating Gate를 생략할 수 있는 CTF를 선택할 수 밖에 없습니다.

삼성은 2016~17년에 1Tbit를 실현한다고 합니다.

현 용량의 8배입니다.

아래 로드맵을 보면 그 때쯤이면 64단으로 현재에 비해 2배입니다.

용량을 8배로 하려면 다이가 커져야겠지요.

현재 24단으로 적층했음에도 용량이 두 배 밖에 늘어나지 않은건 공정이 복잡해짐으로써 상승한 비용을 작은 다이사이즈로 상쇄하기 위함이 아닌가 싶은데,

그렇다면 이후에 공정 상황에따라 다이사이즈가 커질 가능성도 있겠지요.

아무래도 A가 삼성같습니다. 3D 낸드가 제일 빠르니까요.

B는 도시바인듯. 19nm 얘기가 가장 먼저 나온게 도시바입니다.

(삼성이 최대 선폭을 기준으로 공정을 밝히는데 반해 도시바는 최소 선폭을 기준으로 공정을 발표해서 저 수치를 그대로 믿으면 안 된다는 얘기도 있습니다만 뭐 그건 여담......)

- 3차원 수직적층. 24단.

공정미세화가 한계에 다다른 이상 용량을 늘리기위해서는 적층수를 늘리는 방법이 최선일겁니다.

EUV 노광 장비가 본격적으로 쓰이기 전까지는 말이지요.

이번 3D V-NAND 양산 덕에 낸드플래시에서 EUV 장비쪽은 고려하지 않는다는 얘기도 있습니다.

공정상의 어려움도 있을테니 당장 늘어날 것 같지는 않고 점차적으로 최소 두배까지는 늘릴 것으로 예상합니다.

24단에서 48단으로 바로 넘어가기는 힘들테니 중간에 32단이나 36단 정도를 한 번 거쳐서 갈듯 합니다.

여기서 더 나아간다고 가정하면 60단이나 64단이 될 가능성도 있을듯.

2013.08.19.

32 -> 48 -> 64 -> 96 인가 봅니다.

- V-NAND 기반 SSD 발표.

좌측의 V-낸드 SSD는 다이당 128Gbit(=16GB)에 채널당 4다이, 8채널이면 960GB(1024GB)이고,

그림은 4채널뿐이니 용량이 절반은 480GB 제품일겁니다.

8채널로 표시한 것으로 보아 일단 비교 기준은 960GB인 것 같네요.

비교대상인 Planar 낸드 SSD의 용량을 (이것만 봐서는) 알 수 없으나 아마도 같은 MLC 512GB인듯 합니다.

기판봐서는 SSD840 PRO같은데 최대 용량이 512GB였습니다.

(왼쪽 이미지는 진짜 V-NAND SSD 이미지라기보다는 제품 구성을 보여주기위한 예시라고 봐야겠지요.)

최근에 나온 SSD840 EVO 라인업에는 1TB가 있는데 기판 형태가 다릅니다.

SSD840 PRO에 들어간 낸드플래시가 21nm MLC인데 다이당 최대 용량이 64Gbit입니다.

채널당 8다이, 8채널이면 총 용량이 512GB입니다.

(다양한 방향의 해석이 같은 결과를 보여주네요.)

기존 제품 대비 쓰기속도 +20%, 소비전력 -40%

-

- Applied Materials가 핵심 제조 기술을 제공.

(http://pc.watch.impress.co.jp/docs/column/kaigai/20130823_612339.html)

Applied Materials는 3D 낸드 플래시 제조 공정 기술 개발에 대해 주요 낸드업체와 협력해왔다고 합니다.

아래는 2013 Analyst Meeting에서 공개한 슬라이드.

3D 낸드 제조에서 어려운 점은 Etch와 Deposition.

자사의 에치기술은 AVATAR를 통해 높은 A/R을 구현했다고 합니다.

삼성 V-NAND 채널의 A/R은 40:1 정도입니다.

3D 낸드의 제조원가 비율.

제조비용이 올라갑니다만 용량밀도를 높일 수 있기때문에 결과적으로 더 싸다고 볼 수도 있습니다.

16층으로 만들면 가격경쟁력이 없기때문에 24층이 필요하다는 의견이 나왔다고 하는데, 이런 제조비용때문인 것으로 보입니다.

자사 기술을 제공중인 회사를 공개했는데 애초에 낸드플래시 제조사가 4개입니다.

삼성, 도시바, SK 하이닉스, 마이크론.

주요 제조사를 모두 고객으로 두고 있는겁니다.

반응형

'반도체 강좌' 카테고리의 다른 글

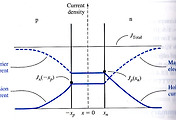

| 반도체 강좌. (7) PN 다이오드(Diode) 전류 특성. (147) | 2013.04.16 |

|---|---|

| 반도체 강좌. (6) PN접합 (PN junction) 수식편. (21) | 2013.04.15 |

| 반도체 강좌. (5) PN접합 (PN junction) 개념편. (183) | 2013.04.14 |

| 낸드플래시(Nand Flash)에 대해 알아봅시다. (113) | 2013.04.10 |

| 반도체 강좌. (4) Nonequilibrium Excess Carriers (48) | 2013.01.05 |

댓글