http://www.chipworks.com/blog/technologyblog/2012/12/11/a-review-of-tsmc-28-nm-process-technology/

TSMC는 파운드리 최초로 28nm 공정 상업파운드리를 시작했습니다.

2012년 1분기, 5% 에 불과했던 매출비중도 4분기는 20% 이상으로 증가했을 것으로 예상됩니다.

(물론 그 바탕에는 AMD, Nvidia 등의 업체들과 소비자의 피눈물이...)

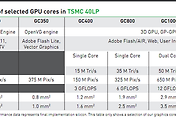

TSMC의 28nm 공정은 크게 4가지입니다.

이 중 현재 나오고있는 것은 HP, HPL, LP 이고, HPM은 실물이 확인되지 않고 있습니다.

- Xilinx XC7K325T Kintex-7

28nm HPL 공정.

High-K Metal Gate (HKMG)

PMOS Gate electrode - TiN (질화티타늄, Ti + N)

NMOS Gate electrode - TiAlN (질화알루미늄티타늄, Ti + Al + N)

Gate dielectric - 2nm SiO2 + HfO2

Gate last - 폴리 게이트로 트랜지스터 완성 후, 소스/드레인 공정이 모두 끝내고 폴리게이트를 제거하고 금속으로 대체. 방식 자체는 인텔과 비슷

- Altera 5SGXEA7K2F40C2 Stratix V

28nm HP 공정.

High-K Metal Gate (HKMG)

기본적으로 HP 공정과 동일하지만, HP 공정에 적합하도록 SiO2 층이 1.2nm 로 감소.

- AMD 215-0821060

AMD HD7970 Tahiti 코어의 6T-SRAM cell

28nm HP 공정.

High-K Metal Gate (HKMG)

면적은 0.16 µm2

90nm 공정이었던 Radeon X1950 Pro SRAM cell 면적이 0.86 µm2

- Qualcomm MSM8960 Snapdragon S4

28nm LP 공정.

TSMC 28nm 공정 중 처음으로 사용가능했던 공정.

Poly/SiON (Poly-silicon/Silicon Oxy-Nitride)

Gate electrode - Poly-silicon

Gate dielectric - SiON

기본적으로, 40nm LP Shrink + e-SiGe (임베디드 실리콘게르마늄)

e-SiGe - PMOS 성능 향상.

'스마트폰 > 기타업체 ETC' 카테고리의 다른 글

| LG H13 (PowerVR 시리즈6 탑재)과 OpenGL ES 3.0 시연. (8) | 2013.01.15 |

|---|---|

| 테이크 LTE (KM-E100) 간단 사용기. (10) | 2012.12.27 |

| Huawei K3V2 GPU 정보/분석. (4) | 2012.09.24 |

| 소니 PS 비타 프로세서에 Wide I/O 메모리 사용. (4) | 2012.07.24 |

| 팬택의 차기 플래그쉽 스마트폰?? IM-A850 (10) | 2012.07.12 |

댓글