- 공정 비교자료 업데이트입니다. (2017.11.29. 기준)

이전에는 삼성, TSMC만 다뤘는데 인텔, GF 자료도 포함할만한 수준이 되어서 범위가 늘어났습니다.

면적, 전력, 백엔드 피치, CELL 사이즈같은건 자료를 하나로 묶기 힘들어서 보류 중.

- 삼성

파운드리 포럼에 자료가 대량으로 풀렸습니다.

대부분 텍스트로만 올라오고 슬라이드는 거의 없는데 중국쪽에는 그냥 다 올려버렸더군요.

그동안 의혹(이라고 하기도 뭐하지만... 10LPU = 8LPP 아니냐 같은거라서.)을 해소하는 로드맵.

그동안 크고 작게 언급됐던 공정들은 다 개별공정이었습니다.

7nm Arfi는 없습니다.

Risk Production이 8LPP가 17년 말, 7LPP가 18년 중순입니다.

간단히 말해서 갤S9 AP 공정은 7LPP가 될 수 없습니다. (갤S9가 상반기 출시이니.)

성능게인

14LPE -> 14LPP : +14%

14LPP = 14LPC -> 14LPU : +15%

10LPE -> 10LPP : +10%

10LPP -> 10LPU : +5%

14LPP -> 11LPP : 성능 +15%, 전력 -30%, 면적 -10%

28FDS -> 18FDS(FD-SOI) : 성능 +20%, 전력 -40%

(링크 : https://pc.watch.impress.co.jp/docs/news/event/1064087.html)

10nm -> 7nm CMOS FinFET : 성능 +20%, 전력 -35%

- TSMC

예전에 해외 기사로 올라왔던 내용이 재확인.

16FF+ -> 7nm : 성능 +35%

뉘앙스로 보면 ArFi 버전 기준인거 같은데 그렇게 잡기에는 성능 향상치가 너무 높아서 EUV 버전 기준으로 보고 반영했습니다.

(다른 내용하고 교차 검증시에도 그 쪽이 그나마 맞아들어갑니다. TSMC 7nm 공정 성능이 예상보다 별로라는 찌라시도 있고요.)

28HPC -> 28HPC+ : 성능 +15%

28HPC+ -> 22ULP : 성능 +15%

- GF

차기 공정 얘기가 좀 나왔습니다.

14LPP -> 12FDX : 성능 +30%

14LPP -> 7LP : 성능 +40%

14LPP -> 12LP : 성능 +10%

22FDX -> 12FDX : 성능 +26%, 전력 -47%

28HPC+ -> 22FDX : 성능 +32% (Body Bias 조건 +49%)

28HPC+ -> 22ULP : 성능 +15%

28HPC+ -> 22FFL : 성능 +35%

위 사진은 나온지 좀 된거고 이게 최근에 나온겁니다.

기준이 28HPM으로 바뀌었지요.

이 부분이 앞뒤가 안 맞아서 값을 정하기 어려운데 뒤에서 다루겠습니다.

28HPM -> 22FDX : 성능 +55%

28HPM -> 22ULP : 성능 +20%

28HPM -> 22FFL : 성능 +35%

IBM이 언급한 내용. 10nm -> 5nm GAA FET(Gate All Around FET) : 성능 +40%, 전력 -75%

- 인텔

GF 자료 덕에 포함시킬 수 있게 됐는데 그 덕에 GF 공정 값에 좌지우지됩니다.

22FFL 공정 외에 10nm, 14nm 공정은 다른 공정과 성능 비교 자료가 아직까지 보이지 않아 포함시키지 못 했습니다.

22FFL -> 22FFL+ : 성능 +20%

- 45nm~28nm 성능 게인

기존과 같습니다.

- 16nm~12nm 성능 게인

- 10nm~7nm 성능 게인

차트 길이때문에 잘랐지만 16nm~7nm 공정 간의 성능 관계가 엮여있기때문에 함께 설명하겠습니다.

TSMC는

16FF+ -> 7nm : 성능 +35%를 7nm EUV로 반영.

16FFC는 16FFC -> 7nm EUV : 성능 +33% 라는 기존 내용으로 역산.

10FF, 7nm ArFI, 7nm EUV 성능 차이가 각각 10%라는 내용으로 역산.

삼성은 발표를 그대로 반영.

8LPP는 성능 자료가 없는데 14LPU와 11LPP를 보면 성능은 같고, 면적이 감소하는 패턴입니다.

10LPU와 8LPP도 같은 패턴일 가능성이 높다고 보고 같은 성능으로 추측하였습니다.

10nm -> 7nm CMOS FinFET : 성능 +20%, 전력 -35%

TR 성능 만의 내용인지 전체 칩에 대한 내용인지 모르겠지만 일단 그대로 반영.

10LPE를 기준으로 잡는게 가장 적절한 값이 나오는듯 합니다. (127 x1.2 = 152)

10nm -> 5nm GAA FET(Gate All Around FET) : 성능 +40%, 전력 -75%

이건 GF, IBM에서 나온 내용입니다만 삼성과 완전히 별개의 얘기로 볼 수 없습니다.

(저 셋은 일단 Research Alliance partner 니까요.)

여기서는 5nm로 얘기했지만 삼성 로드맵에서는 4LPP부터 GAA가 적용된다고 했으니 삼성 공정에 맞춘다면 4LPP에 대한 얘기로 해석할 수 있을듯 합니다.

10LPE 기준으로 잡는게 적절해 보입니다. (127 x1.4 = 178)

GF도 발표치를 그대로 반영했습니다.

다만 기존에 다소 과장된 수치를 남발했던 이력이 있어서 실제 어떨지는 두고 볼 일입니다.

- 22nm~18nm 성능 게인

가장 문제가 되는 구간입니다.

일단 18FDS는 삼성 발표치를 그대로 넣었습니다.

다른 업체 22nm 공정보다도 낮은 값이라서 오히려 낮게 발표한게 아닌가 싶을 정도입니다.

앞에서 나왔던 내용을 다시 보면

기존 자료

28HPC+ -> 22FDX : 성능 +32% (Body Bias 조건 +49%)

28HPC+ -> 22ULP : 성능 +15%

28HPC+ -> 22FFL : 성능 +35%

최근 자료

28HPM -> 22FDX : 성능 +55%

28HPM -> 22ULP : 성능 +20%

28HPM -> 22FFL : 성능 +35%

위에서는 28HPC+ -> 22ULP : 성능 +15%라는 TSMC 주장을 그대로 썼습니다.

위 아래 내용에 일관성이 있다면 22FDX 기준으로 28HPM -> 28HPC+ 성능 +15% 인데,

밑에서는 28HPM -> 22ULP : 성능 +20% 입니다.

이러면 28HPC+ -> 22ULP에서 성능 +4% 라는게 됩니다.

+55%가 Body Bias 조건 기준이라고 해석하는 방법도 있는데 이러면 28HPM -> 28HPC+ 성능 +4%가 됩니다.

이러면 TSMC 주장과 충돌이 일어나서 28HPC 성능이 28HPM보다 낮게 되는데, 비슷한 수준이면 모를까 10% 이상 낮아지는걸 납득하기는 어렵지요.

교차검증이 안 되는 상황인데 결국 22nm 공정 성능 게인이 100 내외로 비슷할 것이라는 가정하에 최대한 숫자를 끼워맞춘게 위의 차트입니다.

(GF, TSMC의 발표치 과장을 의심할 수 밖에 없습니다. 아니면 성능의 기준이 다를 가능성도 있고요. 기준 전력이 다르거나 로직, 셀 비율에 차이가 있든가 등등.)

앞서 나온 22FDX -> 12FDX : 성능 +26% 를 통해서 역산한 22FDX 값이 118

이 값을 기준으로 최근 GF 자료, 인텔 자료로 22FFL, 22FFL+ 값을 계산.

TSMC 공정만 놓고보면 22FDX 값 118, 기존 GF 자료, TSMC 자료가 서로 들어맞는 편이라서 이 쪽을 선택.

- 순서대로 모아놓으면

- 2017.12.03. update

TSMC 7nm 표기 수정.

삼성 7LPP, 4LPP 추가.

'스마트폰' 카테고리의 다른 글

| 파운드리 공정 비교. (2018.02.24.) (18) | 2018.02.24 |

|---|---|

| 삼성, TSMC 공정 비교. (2017.03.28.) (9) | 2017.03.28 |

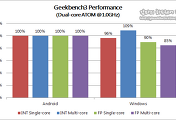

| 긱벤치3를 통한 베이트레일 성능 비교. (update 2014.01.27) (17) | 2013.09.15 |

| 2013.08.31. IT 관련 단신 모음. (6) | 2013.08.31 |

| 엑시노스5410/스냅드래곤800/테그라4 CPU 성능비교. (2013.08.05. Update) (14) | 2013.08.05 |

댓글