- 2/22 부터 ISSCC 2015가 시작되었습니다. (ISSCC : IEEE International Solid-State Circuit Conference)

삼성전자 반도체총괄 김기남 사장의 기조 강연이 있었다고 합니다.

주제는 'Silicon technologies and solutions for the date-driven world' 이라고 하는데 사실 그것보다 궁금한건 지금 기술 개발 상황이 어떻냐는 것.

그런 관점을 중심으로 내용 요약해보겠습니다.

(추가 내용이 나오면 본문에 추가 예정.)

- 출처는 여기.

(링크 : http://techon.nikkeibp.co.jp/article/EVENT/20150224/405720/?ST=silicon&P=1)

발표 내용이 상세하게 잘 소개해주는 편인데 회원이 아니면 글보기가 제한적이고 회원가입 절차도 복잡.

- 정리

5nm까지 근본적인 기술적 어려움은 없다. 그 이하도 가능.

-> 소자 연구 개발 단계에서 삼성은 3.8nm FInFET의 동작을 확인.

-> 노광기술은 EUV와 쿼드패터닝을 결합하면 3.5nm가 실현 가능.

-> 레지스터 기술은 현재 8nm에 머물러 있지만, EUV용 레지스터 재료를 개발 중.

7nm까지는 FinFET으로 미세화가 가능.

-> 그 이상은 GAA(gate all around) 기술, 터널 FET 등이 주류가 될 것.

DRAM

-> 현재 20nm대 이지만 10nm대도 가능.

NAND

-> 현재의 Planar NAND 기술은 더 이상 미세화하면 소자 주위와의 용량결합(parasitic capacitance 결합)이 급속히 커지기때문에 10nm대에 머물고 있음.

-> GAA 기술 중 Vertical NAND(V-NAND)는 주위와의 용량결합이 작은 기술.

-> 3차원 실장에 있어 고밀도화, 멀티비트화(주 : MLC, TLC처럼 한 셀에 여러비트를 저장하는 것)에 유망.

-> 2015년에서는 40층 이상, 더 미래에는 100층이상 1Tbit의 3차원 V-NAND 칩도 개발할 수 있음.

(3차원 V-NAND의 다층화는 2013년 24층, 2014년 32층)

이미지 센서

-> 최근 ISOCELL 기술은 화소가 1.1um 피치인 이미지 센서를 개발.

(ISOCELL : RGB 서브픽셀 사이에 차단층을 만들어 서브픽셀 간 크로스토크, 광유출을 방지하는 기술)

-> 소니의 이면조사기술 다음 단계에서 소니보다 앞섰다며 자신감을 내비침.

'단신 > 단신' 카테고리의 다른 글

| GEN2WAVE RP1600 (Exynos5430) (13) | 2015.03.20 |

|---|---|

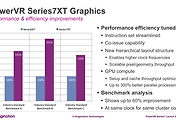

| 심심풀이로 보는 애플 (가칭) A9 GPU 성능 및 사양 추정 (8) | 2015.03.12 |

| 삼성 엑시노스 7890 개발 중? (Exynos 7890) (18) | 2015.02.10 |

| 엑시노스5433 64bit 지원관련 단신. (15) | 2015.02.05 |

| 갤럭시 노트4 S-LTE에 대한 단상. (22) | 2015.01.03 |

댓글