- 갤럭시S22 커널발 퀄컴 스냅드래곤 관련 내용.

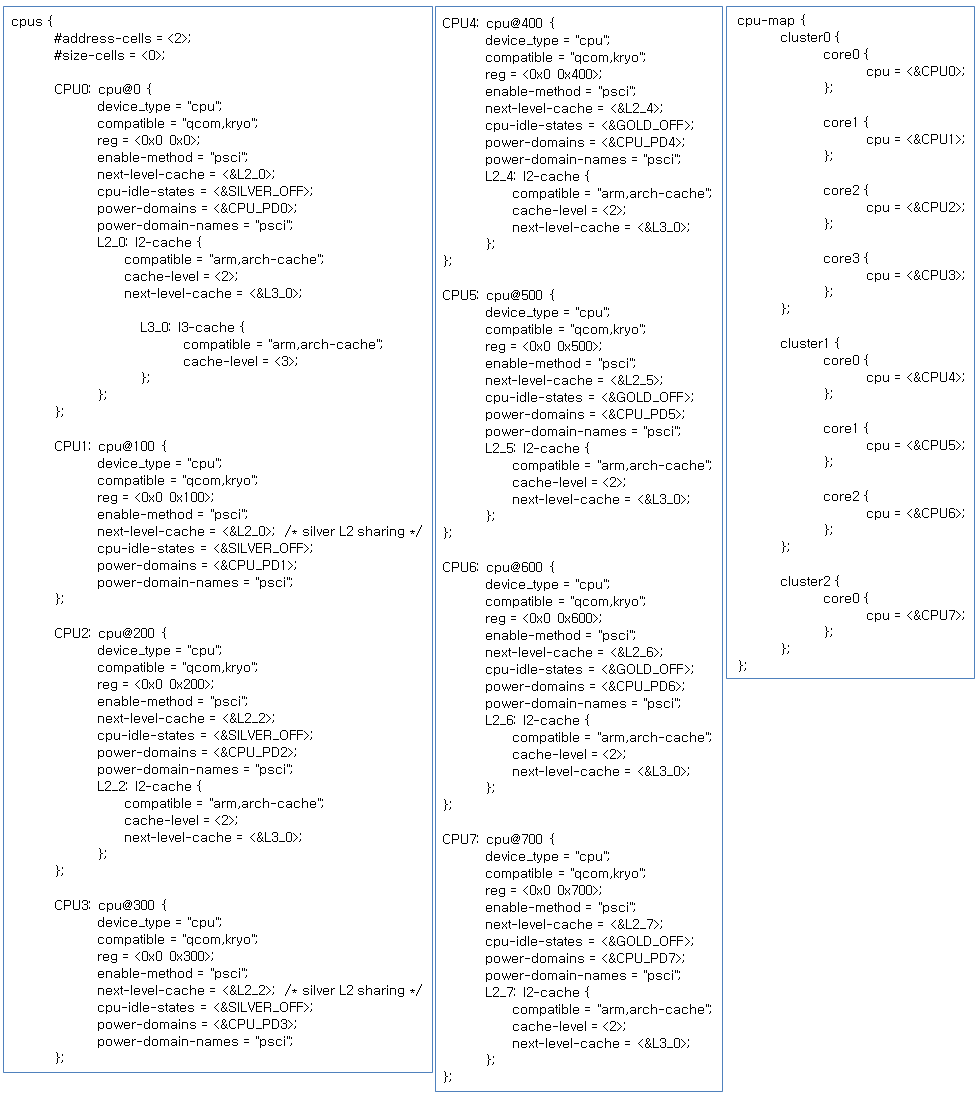

- 스냅드래곤 8gen1 (SM8450, waipio)

알려진대로 코드네임 waipio

초기버전

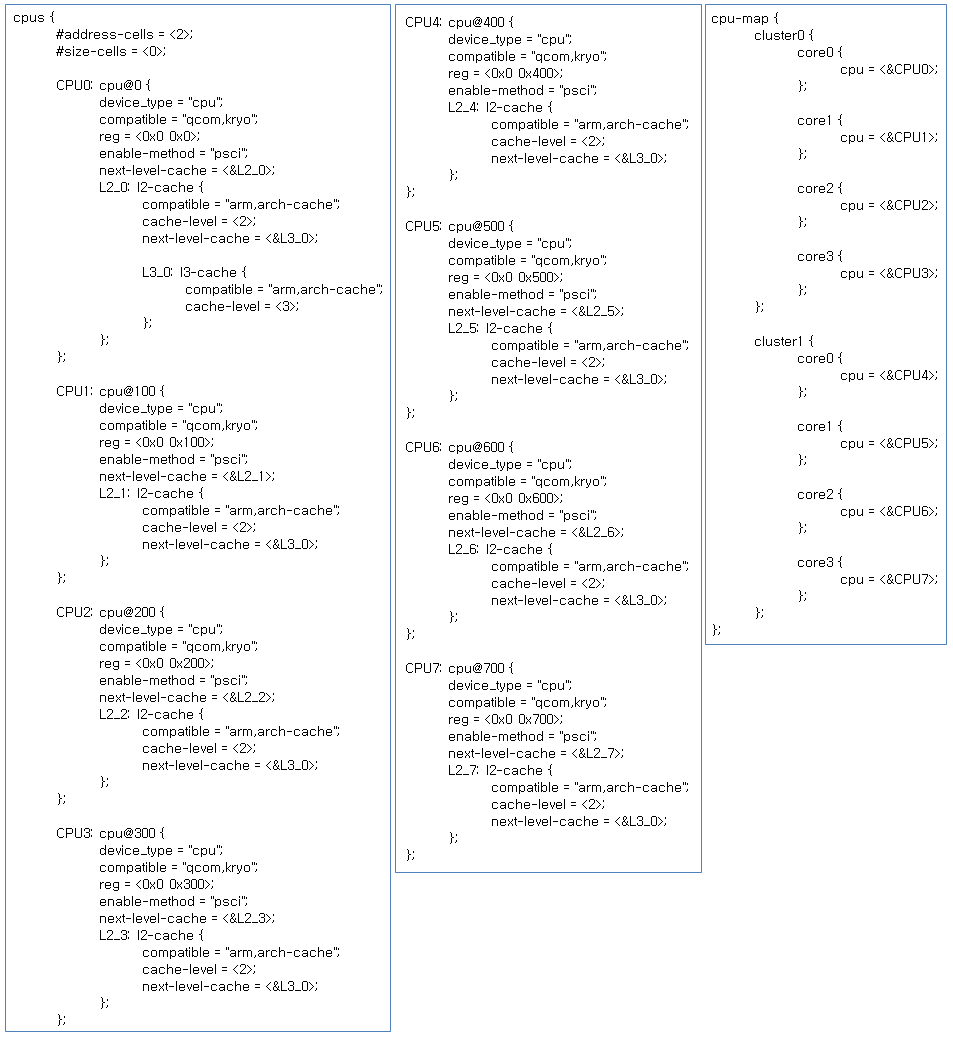

빅코어 x1 최대 2.4GHz + 미들코어 x3 최대 2.4GHz + 리틀코어 x4 최대 1.8GHz

캡쳐는 없지만 다른 파일보면 메모리는 최대 3200MHz

리틀코어 2코어마다 L2 캐시 공유, 빅/미들 각 코어는 독립 L2 캐시, ALL 코어 L3 캐시 공유.

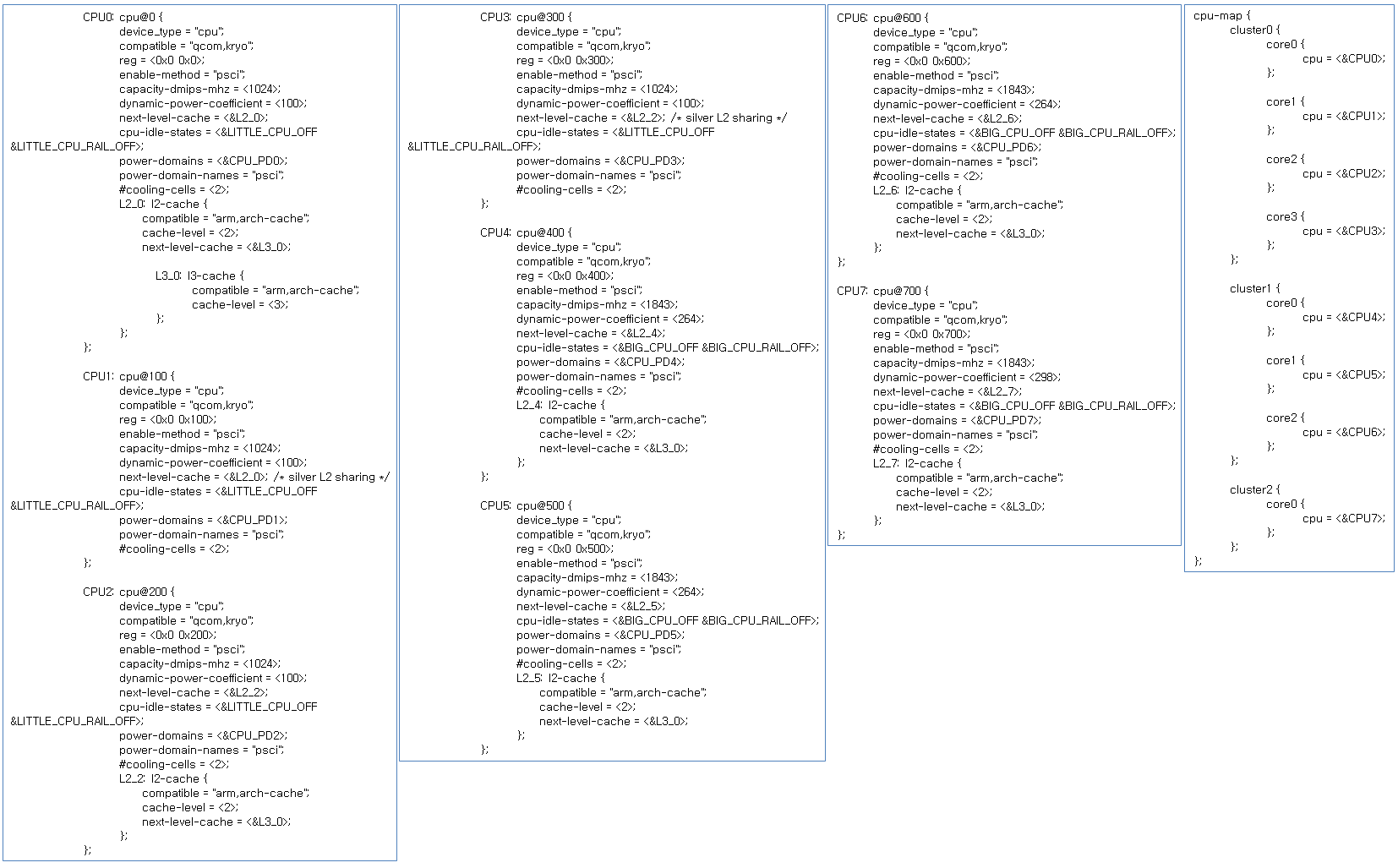

빅코어 : capacity-dmips-mhz 2386 / 다이나믹 전력 상수 396

미들코어 : capacity-dmips-mhz 2235 / 다이나믹 전력 상수 251

리틀코어 : capacity-dmips-mhz 1024 / 다이나믹 전력 상수 100

GPU 최대 818MHz

V2 버전 (이게 현 출시버전인듯.)

이전 버전 대비 변경점만 보면

빅코어 x1 최대 3.0GHz + 미들코어 x3 최대 3.0GHz + 리틀코어 x4 최대 1.8GHz

빅코어 : 다이나믹 전력 상수 396 -> 450 증가

미들코어 : 다이나믹 전력 상수 251 -> 259 증가

GPU Adreno730v2(gen7-0-1)로 변경, 클럭 동일.

V2 기준으로 보면

capacity-dmips-mhz 비는 빅 : 미들 : 리틀 = 2386 : 2235 : 1024 = 2.33 : 2.18 : 1

스냅888 대비 빅, 미들코어 성능을 크게 잡았음.

(스냅888이 2.0 : 1.9 : 1 , 엑시노스2100이 3.83 : 3.38 : 1 , 엑시노스2200이 1.87 / 1.46 / 1)

코어 성능 셋팅만 보면 엑시노스-스냅이 전 세대(스냅888-엑시노스2100)와 반대가 됨.

전력 상수는 엑시노스와 수치 그대로 비교는 어려울듯 하고 비율로 보면

8gen1 - 빅 : 미들 : 리틀 = 450 : 256 : 100 = 4.50 : 2.56 : 1

엑시노스2200 - 빅 : 미들 : 리틀 = 765 : 560 : 189 = 4.05 : 2.96 : 1

(링크 : 엑시노스 커널 정보. (갤럭시S22))

공정 차이가 작지만 있고 엑시노스 빅코어 클럭이 상대적으로 낮아서 전력효율이 좋아진듯한데,

미들코어는 클럭차이도 거의 없는데 엑시노스가 더 안 좋은건 퀄컴이 설계에서 차이를 둔걸지도.

아니면 리틀코어 특성이 같은거라는 가정인데 사실 그렇지 않을지도.

- cape

빅코어 x1 + 미들코어 x3 + 리틀코어 x4

리틀코어 2코어마다 L2 캐시 공유, 빅/미들 각 코어는 독립 L2 캐시, ALL 코어 L3 캐시 공유.

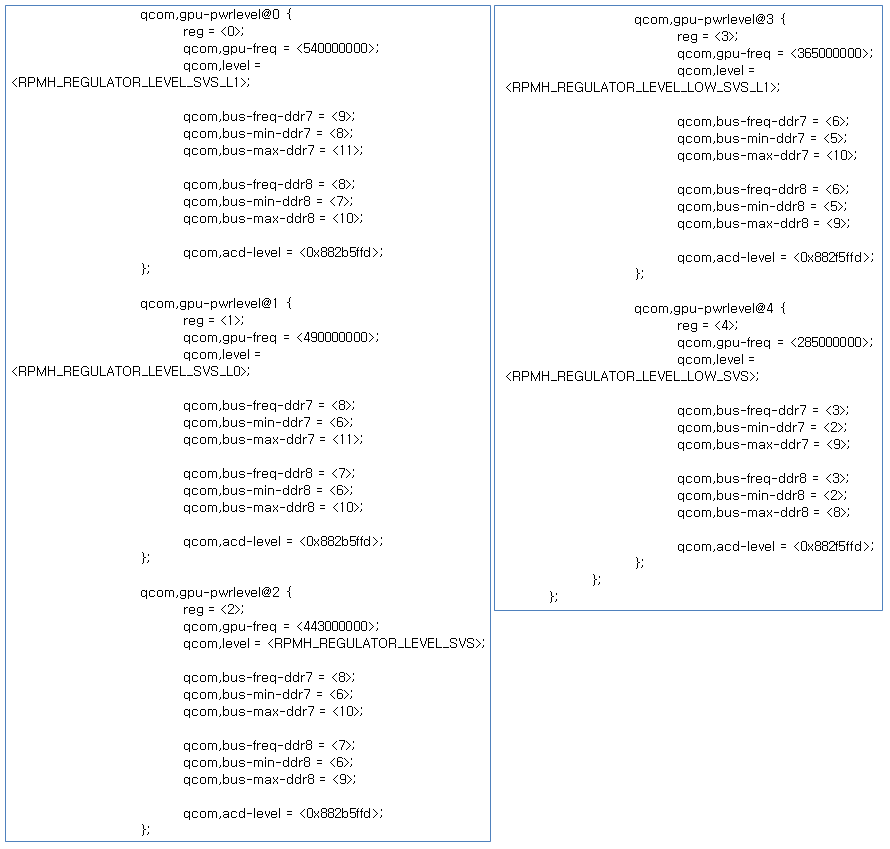

- diwali

빅코어 x1 + 미들코어 x3 + 리틀코어 x4

리틀코어 2코어마다 L2 캐시 공유, 빅/미들 각 코어는 독립 L2 캐시, ALL 코어 L3 캐시 공유.

빅코어 : capacity-dmips-mhz 1843 / 다이나믹 전력 상수 298

미들코어 : capacity-dmips-mhz 1843 / 다이나믹 전력 상수 264

리틀코어 : capacity-dmips-mhz 1024 / 다이나믹 전력 상수 100

GPU 최대 540MHz

빅/미들코어 성능 값이 같은 점, GPU 클럭이 낮은 점을 봐서 스냅700 라인으로 추측.

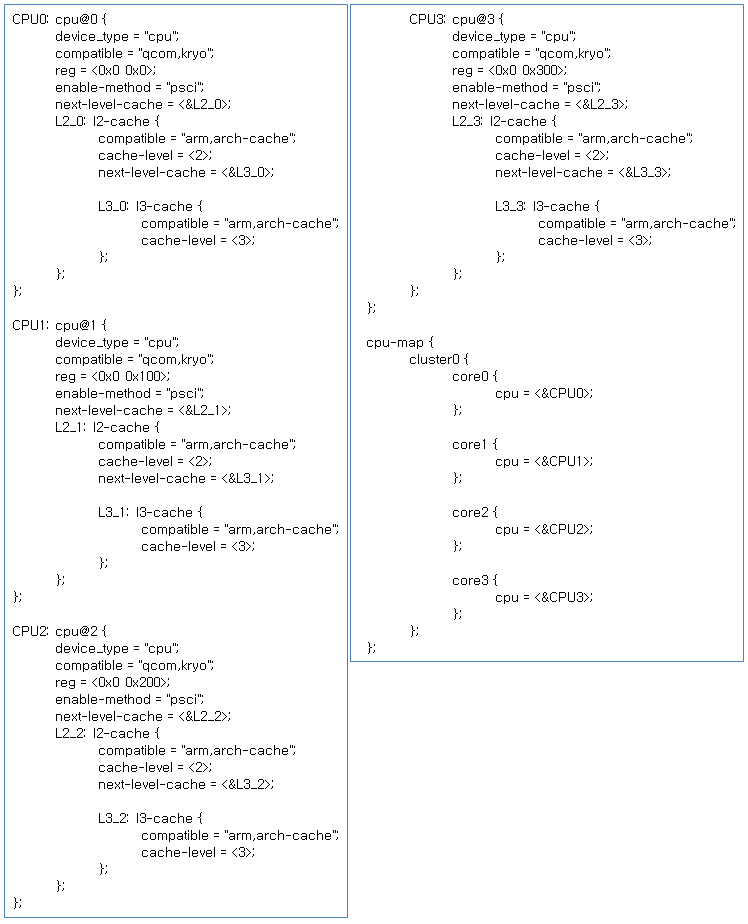

- neo

4코어, 각 코어 독립 L3 캐시.

스마트폰, WoA, 서피스 플랫폼같은 일반 모바일 제품에 쓰기에 4코어는 코어 개수가 너무 적고,

웨어러블에 들어가자니 L3 캐시가 공유 캐시가 아닌게 특이하고 과잉 사양으로 보임.

(루머에 퀄컴이 차기 웨어러블용 SoC에도 Cortex-A53을 쓴다고 하는데 CA53 단독 탑재 사양에서 L3 캐시가 들어간 경우가 거의 없음.)

현재로는 가장 유력한 용도는 automotive용도가 아닐까 추측되고, 그렇다면 그동안 기존 모바일용 칩을 활용하는 단계에서 벗어나서 전용 칩을 만드는 단계로 넘어간걸로 볼 수 있음.

- parrot

4+4코어, 각 코어 L2 독립캐시, All 코어 L3 공유 캐시

위의 일반적인 제품들과 다르게 0~3코어 L2캐시가 2코어 공유가 아닌데, 리틀코어 아키텍처가 아닐 가능성이 높아보임.

그러면 이전 사례로 보아 빅코어 + 빅코어 구성이고 컴퓨트 플랫폼(WoA, 서피스) 용도로 추측.

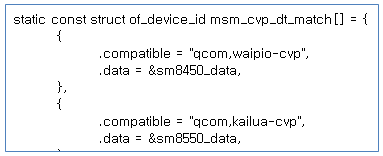

- kailua (SM8550)

SM8550(8 gen2 ?) 코드네임은 kailua

이전 플래그십들과 마찬가지로 하와이 지명.

루머나 분위기상 존재가 기정사실 상태인 SM8475(TSMC 4nm 공정 8 gen1)에 대한 정보는 보이지 않음.

다만 waipiop(waipio plus), waipiop v2에 대한 파일은 있는데 파일명만 있고 내용은 거의 없어서 이게 SM8475인지 어떤지 아직은 불명.

'스마트폰 > 퀄컴 Qualcomm' 카테고리의 다른 글

| 긱벤치 ML을 통한 Adreno GPU 사양 추정. (A7x, A6x, A5x) (update 23.11.05.) (8) | 2023.10.24 |

|---|---|

| 퀄컴 제품 코드네임 정보. (갤럭시S23 커널발, 230228) (0) | 2023.02.28 |

| 퀄컴 차기 플래그십 스냅드래곤 긱벤치5 초기 결과 (SM8450) (5) | 2021.09.05 |

| 스냅드래곤 커널 정보. (갤럭시S21 커널, LAHAINA, CEDROS, SHIMA, YUPIK, HOLI) (0) | 2021.01.28 |

| 퀄컴 스냅드래곤875 긱벤치5 초기 결과. (SDM875G, Geekbench5) (17) | 2020.11.08 |

댓글