팹리스, 파운드리 단신. (2023.11.10. 인텔, 구글, AMD, 삼성)

- 퍼갈 때 2차 출처 표시바람.

- 삼성

삼성 GPU RTL

이전 포스팅에서 Xclipse 시리즈가 계속 AMD IP를 사용하고 있고, 삼성 자체 커스텀은 없는 것으로 추측된다고 썼는데,

이것이 마치 삼성에서 설계에서도 이렇다 할 역할이 없는 것처럼 해석될 수 있어서 그렇지 않다는걸 소개하는 것임.

(팹리스, 파운드리 단신. (2023.10.27. 삼성, 구글, 퀄컴))

삼성 GPU 기능 추가. (Occlusion Query, Data Sharing Protocol)

new features라는 것과 기간을 봐서는 Xclipse930까지는 없던 기능같은데, 이름만 보면 지금까지 하드웨어적으로 없었다는게 의아한 기능들임.

모바일에 탑재하는데 제약이 있었다든가 하는 이유가 있었을지도 모르겠음.

- AMD

AMD 삼성 4nm 공정 작업.

TSMC 3nm도 같이 표기되어 있는데 해당 공정을 쓰는걸로 알려진 AMD 제품은 현재까지 서버용 Zen5 코어 밖에 없음.

(팹리스, 파운드리 단신. (2023.04.08. AMD, 삼성, 퀄컴, 인텔))

그렇다면 삼성 4nm 공정 제품도 서버용 I/O 다이같이 Zen5 서버와 관련된 제품일 가능성을 생각해볼 수 있을듯.

AMD 코어 코드네임 Nirvana, Prometheus

Nirvana는 Zen5 코어 코드네임으로 확인됐음.

(팹리스, 파운드리 단신. (2023.04.08. AMD, 삼성, 퀄컴, 인텔))

Zen5와 묶여있는걸보면 Prometheus는 Zen5c 코드네임일 가능성이 있을듯.

다만 그렇다면 니르바나라는, 그리스 로마 신화와 관계없는 코드네임 갑자기 나오는 바람에 코드네임의 일관성이 없어져서 프로메테우스와 엮을만한 상상력을 발휘하기가 어려워짐.

Zen4-Zen4c 코드네임이 Persephone-Dionysus인데 디오니소스가 페르세포네의 자식이라는 판본도 있어서 코드네임 관계가 납득이 되는 것과 비교됨.

그 내용 중에 프로메테우스가 잠시 등장하는데 이것에 의미를 부여하면 Zen5c는 Zen5의 다운그레이드가 아니라 Zen4c의 발전형일거란 가설이 가능할듯.

- 퀄컴

퀄컴 삼성 3nm 프로젝트.

- 구글

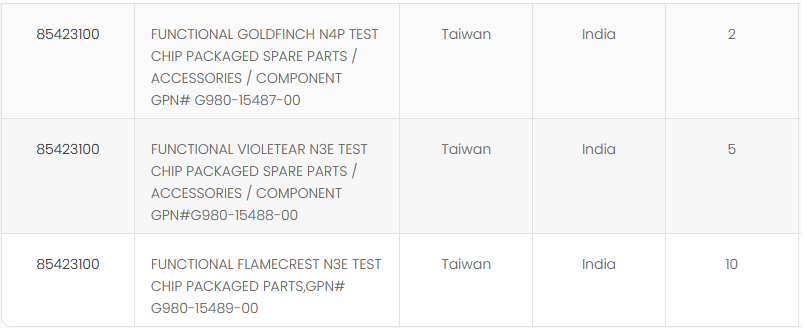

구글 테스트칩.

GPN, 표기양식 등 정보로 보아 구글일 가능성이 매우 높아보임.

N4P 공정 테스트칩 Goldfinch

N3E 공정 테스트칩 Violetear

N3E 공정 테스트칩 Flamecrest

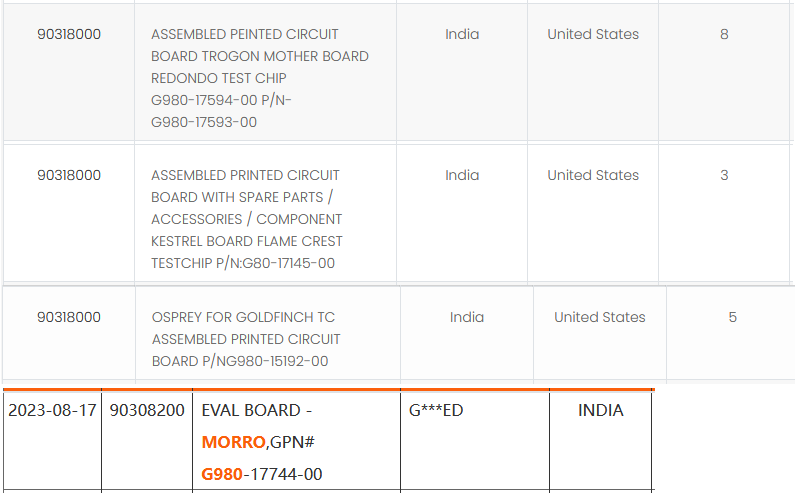

테스트칩 개발보드?

Redondo 칩 - Trogon 보드

Flamecrest 칩 - Kestrel 보드

Goldfinch 칩 - Osprey 보드

? - Morro 보드?

Redondo는 지금은 취소된걸로 알려진 텐서G4의 TSMC 생산시도 제품이고, Morro를 제외한 코드네임은 모두 새(조류)임.

(팹리스 파운드리 단신 (2023.10.13. 퀄컴, 삼성, 구글))

Morro에 탑재된 칩은 다른 칩과 성격이 다른 제품인듯.

어떻게든 텐서와 엮어본다면 Redondo의 테스트칩이 Goldfinch이고, 테스트 보드는 Trogon이고, Violetear, Flamecrest는 후속 텐서라는게 됨.

하지만 그렇다면 Goldfinch - Trogon 이 조합된 이력이 없다는 것이 설명이 안 됨.

못 보던 코드네임 패턴이라서 추가 정보를 기다려봐야할듯.

- 인텔

인텔 삼성 14nm 공정 이용.

이전에 나왔던 내용의 교차검증.

( 파운드리 단신. (2023.02.10. 퀄컴, 메타) )

인텔 TSMC N3E 공정 프로젝트. (Low Jitter PLL)

인텔 GDDR7 프로젝트 (Intel3? Intel4?)

GDDR7 메모리 사용제품이면 기본이 GPU인데 이건 TSMC 공정을 계속 쓸 가능성이 높고, 인텔 공정을 쓰면서 메모리대역폭이 필요한 제품은 GDDR이 아니라 HBM을 사용함.

인텔 CPU, 내장 GPU의 루머, 유출 정보를 보면 세대 변화에 비해 상당히 빠르게 공정 전환이 진행되고 있음.

그렇다면 Xe3나 Xe4 아키텍처쯤에는 TSMC에서 인텔 공정으로 전환될 경우도 생각해볼 수 있는데,

그 때쯤에 Intel3이나 Intel4 공정이 경쟁력을 유지할 수 있을지 의문이 남음.

7nm라고 나와있지만 P1276은 인텔 내부에서는 7nm, 외부에는 Intel4, Intel3으로 말하는 CPU 공정임.

이런 차이가 있음에도 링크드인에서 내,외부 기준없이 사람마다 표기를 혼용하는 바람에 정확히 해석하는데 어려움이 있는데,

조만간 이에 대해 포스팅할 예정임.

위 내용과 같은 작업 내용일지?

HBM3 사양 인텔 서버칩 공정 Intel3, N5, N3

멀티다이 IO 서버칩, HBM3 사양, 공정으로 보아 Ponte Vecchio 후속인 Rialto Bridge에 대한 내용으로 보이는데

Rialto Bridge는 취소되었음.

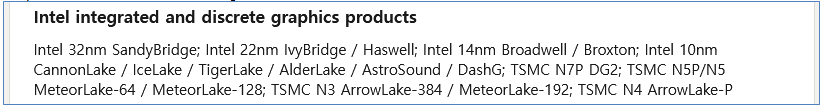

인텔 내장, 외장 그래픽 공정, 사양.

인텔이 내장, 외장을 구분하는 기준이 (일반적으로 생각하는) 메모리를 시스템과 함께 쓰는가, 별도 메모리가 있는가.가 아니라 칩 안에 GPU가 통합이 됐는가, 별도 다이로 분리되어 있는가.로 구분하는 것 같음.

DG2 : N7P

Meteor Lake 64EU : N5P/N5

Meteor Lake 128EU : N5P/N5

Meteor Lake 192EU : N3

Arrow Lake P : N4

Arrow Lake 384EU : N3

DG2(Arc-A)는 N6 공정인데 여기서는 N7P로 표기되었음.

사실 N7 기반 파생 공정이면서 대외적으로 6nm로 마케팅을 했든가, 초기에 N7P 공정으로 시작했다가 최종적으로 N6 공정으로 마무리됐을 가능성이 있을듯.

유출된 자료에 따르면 애로우 레이크 P GPU(GT3)이 N3 공정 320EU인데 최종적으로 384EU로 정해졌다고 볼 수 있음.

자료를 믿는다해도 2년 전 내용이라서 많은 것이 바뀌었을거고 실제 공정 변경에 대한 루머가 나오기도 했음.

다만 그렇다면 왜 굳이 애로우 레이크 P를 별도로 표기했고 그것이 N4 공정이냐가 의문임.

보통 S가 GPU 사양이 가장 낮고 U/P/H는 높아서 384EU를 S 타겟으로 보기는 어려움.

발표된 메테오 레이크 GPU 사양이 N5 공정 최대 128EU인데 N3 공정 192EU가 나타났음.

메테오 레이크 모바일 타겟에 최대 192EU가 들어갈 것이라는 주장이 있고, 그 경우 GPU 다이가 커져서 베이스 다이를 넘어서지만 Foveros Omni를 적용하면 된다는 주장도 있음.

또 메테오 레이크 GPU가 최초에 N3 192EU로 개발하다가 N5 128EU로 바뀌었다는 루머도 있음.

그런 흔적이라고 보는게 타당할듯.

그런 주장도 가능성이 있겠지만 다른 가능성을 생각해보면...

전례를 보면 CPU 세대가 바뀌어도 GPU 아키텍처는 바뀌지 않은 사례가 있는데, 마침 같은 N3 공정에 애로우 레이크 384EU의 절반 사양임.

그리고 U/P/H 라인에서 GPU 최소 사양이 최대 사양의 절반이고, 유출 루머에 따르면 메테오 레이크 U/P/H 라인 GPU는 Xe2 아키텍처 기반에 최대 128EU라고 함.

이를 종합하면 가설을 세워보면

메테오 레이크 GPU(Xe2)는 실제 최대 128EU이고, 이를 기반으로 만든 N3 공정 192EU 사양의 다이는 애로우 레이크 하위 라인에 들어갈 GPU임.

이렇게 가정을 하면 애로우 레이크 P N4도 끼워맞춰볼 수 있는데, 일단 애로우 레이크 P라인에 N3, N4 공정의 2가지 GPU 타일이 있다고 보는게 현재로는 타당함.

그리고 N4 다이의 라인업 포지션을 생각해보면 무조건 N3보다 낮아야함.

N4 공정을 쓰면서 N3 GPU보다 사양이 높으면 면적이 더 커진다는건데 그럴 이유가 없음.

즉, 애로우 레이크 GPU 라인업은 N3 384EU - N3 192EU - N4 96EU? 가 됨.

전례대로면 384EU - 320EU - 256EU - 192EU 의 차이를 두겠지만, 최고 사양의 절반이 중간에 배치되는 형태가 돼서 전례를 따르기는 어렵게 됐고, 최소 사양으로 전 세대(메테오 레이크) 대비 50% 증가한 96EU 정도가 적절한 것으로 생각됨.

클라이언트 타겟으로 타일 기반 3D 적층 제품을 내놓은게 메테오 레이크가 처음이니 앞으로 인텔이 보여줄 조합을 지켜보면 후속 제품 정보 해석의 정확도가 올라갈듯.

인텔 그래픽 공정 TSMC N7+/N5/N4/N3

위에서 인텔이 말하는 내장, 외장 그래픽 구분 기준이 일반적인 인식과 다르다는 해석이 여기에도 잘 들어맞음.

Arc 그래픽 카드의 GPU 공정이 N7+/N5/N4/N3라면 Battlemage가 N5 공정, Celestial이 N4 공정, Druid가 N3 공정이라는게 되는데, 경쟁 외장 그래픽 제품과 비교해서 공정 경쟁력이 없고, 현재까지 파악된 향후 Xe1/2/3 아키텍처 기반의 내장 그래픽 공정과 비교해도 크게 밀려서 이렇게 해석하는건 틀렸다고 봐야함.

Arc-A는 여기서도 N6이 아니라 N7+로 표기되었음.

N5는 메테오 레이크 GPU, N4는 애로우 레이크 GPU, N3는 애로우 레이크, 메테오 레이크 GPU로 위에서 확인됨.